# From Analog to Digital – Part 2: The Conversion Process

| < Previous Next >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                   |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Popular Recent                                                                                                                                                                                                                                                                                    |  |  |

| <ul> <li>From Analog to Digital - Part 1: Introduction</li> <li>From Analog to Digital - Part 3: Signal Sampling</li> <li>From Analog to Digital - Part 4a: Signal Bandwidth</li> <li>From Analog to Digital - Part 4b: Signal Bandwidth</li> <li>From Analog to Digital - Part 5: Signal Conditioning</li> <li>From Analog to Digital - Part 6a: ADC Performance</li> <li>From Analog to Digital - Part 6b: ADC Performance</li> <li>From Analog to Digital - Part 6c: ADC Performance</li> </ul>                                                                                                                   | Using Nutaq's<br>MBDK with GNU<br>Radio – Part 2:<br>Implementing a<br>polyphase<br>channelizer<br>April 4th, 2014<br>Massive MIMO –<br>Part 5: The need<br>for practical<br>prototyping and<br>implementation<br>April 23rd, 2014<br>An FPGA-based<br>AGC algorithm<br>using System<br>Generator |  |  |

| <ul> <li>From Analog to Digital – Part 7: Precautions</li> <li>From Analog to Digital – Conclusion</li> </ul> This blog post is the second in a series presenting an overview of the theories and practices of analog-to-digital conversion. In the previous post, we briefly discussed the recent transition from the infinitely continuous analog world that surrounds us to a discrete digital world where everything is defined as sequences of numbers. Bridging the gap between the analog world and the digital world requires the use of analog-to-digital and digital-to-analog converters (ADCs and DACs). |                                                                                                                                                                                                                                                                                                   |  |  |

| This series of blog posts will focus on the ADCs in order to examine how<br>they work, how to use them properly and how to understand their<br>characteristics and limitations.<br>The first step is to take a look at the two fundamental processes                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                   |  |  |

involved during the analog-to-digital conversion: sampling and quantization.

April 23rd, 2014

# **Sampling and Quantization**

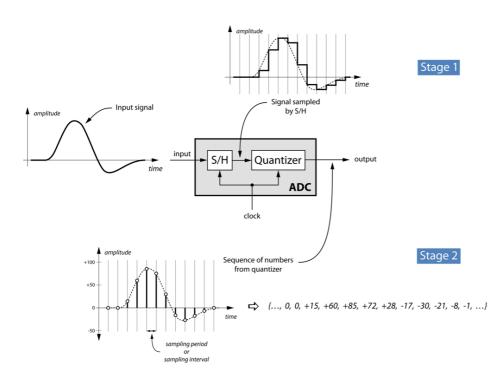

Analog signals that are to be digitized by an ADC normally come from sensors or transducers that capture a signal (sound, pressure, light, radio waves, and so on) and transform it into a voltage that is proportional to the amplitude of that signal. The operation required to convert the voltage generated by the sensor to its digital equivalent is performed by the ADC as a two-stage process. This process is illustrated by the following diagram.

April 24th, 2014 Challenges with massive MIMO: Data throughput

Massive MIMO

mechanics:

Massive

waveform

playback

recording and

April 28th, 2014

# Sampling

The first step (Stage 1 in the diagram) consists of taking an instantaneous snapshot of the ADC's input voltage and freezing it for the duration of the conversion. This is the *sampling* part of the process, and it's performed by the *Sample-and-Hold* (S/H), also referred to as *Track-and-Hold* (T/H), which is located directly at the input of the ADC. The S/H briefly opens its aperture window to capture the input voltage on the rising edge of the clock signal, and then closes it to hold its output at the newly acquired level. As shown in t diagram above, the signal present at the output of the S/H (internal to the ADC and invisible from the outside) has a staircase-like appearance. The output level of the S/H is updated on every rising edge of the ADC's clock input.

## Quantization

The second step (Stage 2 in the diagram) assigns a numerical value to the voltage level present at the output of the S/H. This process, known as *quantization*, searches for the nearest value corresponding to the amplitude of the S/H signal out of a fixed number of possible values covering its complete amplitude range. The *quantizer* can't search over an infinite number of possibilities and must restrict itself to a limited set of potential values. The size of this set corresponds to the range of the quantizer and is always a power of 2 (or  $2^N$ , such as 256, 512, 1024, and so on).

Once the closest discrete value has been identified by the quantizer, it is assigned a numerical value and encoded as a binary number. Since the value is necessarily contained in the complete set of  $2^{N}$  potential values, only N bits are required to represent all the binary encoded numbers that can be generated by the quantizer. For this reason, ADCs are often referred to as *N*-bit ADCs, where N represents the number of bits used by the ADC to encode its digitized values. By convention, *N*-bit is also used to denote the *resolution* of the ADC, since the quantization *step* (the distance between discrete quantization levels) is equal to  $1/2^{N}$ .

By its fundamental nature, the quantization and encoding process cannot be infinitely accurate and can only provide an approximation of the real values present the ADC's analog input. The higher the resolution of the quantizer, the closer this approximation will be to the actual value of the signal. Nevertheless, the conversion process will always introduce systematic quantization errors, which will fall within half the quantization step size (smaller than half a negative step if it rounds off to the nearest value, or smaller than half a positive step if it truncates to the nearest value). Because this error is normally distributed randomly from one digitized sample to the next, it's usually referred to as *quantization noise*.

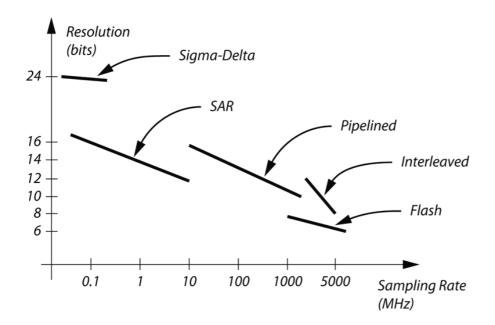

There are multiple constraints that limit the resolution of an ADC, but most of these constraints are related to the time required by the quantizer to determine the closest match for the signal at the output of the S/H. Scanning a larger set of potential values obviously requires more time, so a variety techniques have been developed (and continue to be developed) to accelerate this process. The description of each of these techniques is beyond the scope of this discussion, but the final selection of one technique over the other is usually the result of an elaborate compromise between resolution, sampling rate, cost, and power consumption. The following table summarizes the characteristics you could expect from ADCs that have theoretically perfect performance (which never happens in real life). The table also shows the maximum sampling rate that is currently being supported by the best devices in each category.

| Resolution<br>(in bits) | Range      | ± Range     | Quantization<br>Error | Maximum<br>Sampling Rate |

|-------------------------|------------|-------------|-----------------------|--------------------------|

| 24                      | 16,777,216 | ± 8,388,608 | ± 0.000003%           | 200 KHz                  |

| 16                      | 65,536     | ± 32,768    | ± 0.0008%             | 250 MHz                  |

| 14                      | 16,384     | ± 8,192     | ± 0.003%              | 400 MHz                  |

| 12                      | 4,096      | ± 2,048     | ± 0.012%              | 1.8 GHz                  |

| 10                      | 1,024      | ± 512       | ± 0.05%               | 2.2 GHz                  |

| 8                       | 256        | ± 128       | ± 0.2%                | 3 GHz                    |

| 6                       | 64         | ± 32        | ± 0.8%                | 6 GHz                    |

The following diagram shows the most common ADC techniques currently on the market and where they sit in the spectrum of resolution versus sampling rate. This diagram is by no means accurate nor complete, but is only intended to provide an overview of how each technique is positioned relative to the others. Detailed descriptions of the internal operations of each of these techniques (sigma-delta, successive approximation or SAR, pipelined, interleaved, and flash) can easily be found online.

### **Advantages of Analog-to-Digital Conversion**

But why is there an advantage to digitizing analog signals? After all, what comes out of an ADC is just a sequence of numbers representing a real and continuous signal at discrete moments in time. How can you

get more from less? Well, in this case, you do.

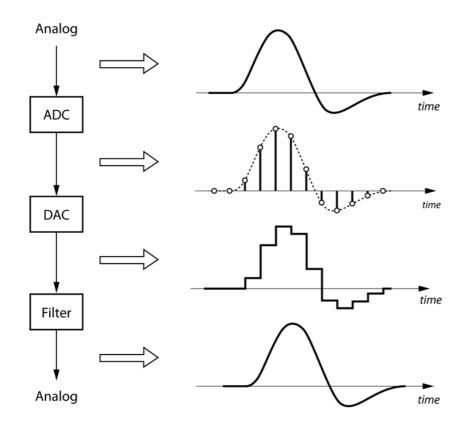

The detailed explanation for this might be quite laborious and revolves around what is known as the *Nyquist-Shannon sampling theorem*. In simple terms, the theorem states that a continuous bandlimited signal (or function) can be completely defined or reconstructed from an infinite sequence of samples defining it. In other words, if we digitize a signal using an ADC with an infinite precision (not limited to N bits), and we then convert the signal back to an analog format using a DAC (digital-

Software

Company

Library

Properly regenerating the analog signal requires the use of an output analog *reconstruction filter* to smooth out the discrete steps present at the output of the DAC.

There are many advantages in working with digitized signals instead of working with them in their original analog format. To list a few examples:

• There is a very large amount of intrinsic data reduction when you only have to work with a limited quantity of information (discrete

Q

samples) instead of a continuous and infinitely detailed signal.

- If handled properly, numbers won't degrade, so digitized information can theoretically last forever (but we won't get into a debate on this).

- Digital numbers are expressed as series of 0s and 1s that can be moved around, stored, transmitted, transformed into other numbers, and so on. As long as information remains in a digital format, it can be manipulated and processed using common media and tools. This can't be said of analog signals, which require dedicated means to process each specific type of signal.

# Conclusion

In this post, we looked at the steps involved in the analog-to-digital conversion process, which acts as the bridge between the analog world and the digital world. Even though the conversion should theoretically be lossless, it has been shown that ADCs have intrinsic limitations in accuracy and sampling frequency that will have an impact on the quality of the conversion. We'll examine the consequences of those limitations, as well as other factors that will also have an influence on the accuracy of the transition from the analog to digital domain, in coming posts.

Watch for our next post in this series, in which we'll discuss signals and bandwidth.

### ABOUT US

Leveraging on decades of digital signal processing (DSP) expertise, we develop and deliver rapid-prototyping, test

### RECENT POSTS

Integrating Custom IP Cores in Nutaq Design Flow: Part I

#### ABOUT NUTAQ

Overview News & Press Releases Investor Relations (NuRAN Wireless)

| and validation solutions that<br>are cutting the time-to-market<br>of our customers, thereby<br>helping fuel next generation's<br>wireless innovations such as<br>software-defined radios (SDR),<br>5G Massive MIMO, CRAN,<br>HetNet and IoT, to customers in<br>the wireless market. | IEEE Paper – Carrier<br>Frequency and Sampling<br>Rate Offsets Effect on Sub 6<br>GHz Massive MIMO<br>Video: PicoLTE with GPS-<br>Disciplined Clock | Careers<br>Contact us |   |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---|----|

| Copyright 2015 Nutaq Innovations   All R<br>Nutaq   Cookie Policy                                                                                                                                                                                                                     | ights Reserved   Powered by                                                                                                                         | f¥                    | V | in |